# Designing a Robust IIoT to SCADA Gateway

### Class 2: Introduction to the RZ/N1

October 23, 2018

Charles J. Lord, PE President, Consultant, Trainer Blue Ridge Advanced Design and Automation

**DesignNews**

Blue Ridge Advanced Design and Automation Asheville, North Carolina

# This Week's Agenda

- 10/22 The Challenges of IIoT and Industrial Ethernet

- 10/23 Introduction to the RZ/N1

- 10/24 Many Protocols, One Abstraction GOAL

- 10/25 Programming the R-IN Protocol Engine

- 10/26 Writing and Testing Our Application

Presented by:

Blue Ridge Advanced Design and Automation Asheville, North Carolina

# This Week's Agenda

10/22 The Challenges of IIoT and Industrial Ethernet

10/23 Introduction to the RZ/N1

10/24 Many Protocols, One Abstraction - GOAL

10/25 Programming the R-IN Protocol Engine

10/26 Writing and Testing Our Application

**DesignNews**

Blue Ridge Advanced Design and Automation Asheville, North Carolina

## Many Protocols, One Chip

- Yesterday we saw that we need to be able to interface with many different protocols, some of which have specific hardware requirements

- Today we will look at the Renesas RZ/N1 family of processors, particularly the RZ/N1D with dual ARM Cortex A7 application processors.

4

| System                | Package                                                                                                                             |                                                                                      |                                                                    | Interface                                       |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------|--|

| 2 x 16 ch DMAC        |                                                                                                                                     | 400-pin LFBGA 17mm x 17mm / 0.8 mm pitch<br>324-pin LFBGA 15mm x 15mm / 0.8 mm pitch |                                                                    |                                                 |  |

| JTAG                  |                                                                                                                                     | CPU                                                                                  |                                                                    | 2 x I <sup>2</sup> C                            |  |

| CGC                   | Arm <sup>®</sup> Cortex <sup>®</sup> - A7<br>Dual Core Processor<br>500 MHz                                                         |                                                                                      | <sup>®</sup> Cortex <sup>®</sup> - A7<br>Core Processor<br>500 MHz | 2 x CAN                                         |  |

| Timer                 | FPU MMU Debug GIO                                                                                                                   | FPU N                                                                                | MU Debug GIC                                                       | 6 x SPI                                         |  |

| 6 x 16 bit GPT        |                                                                                                                                     |                                                                                      |                                                                    | 2 x USB2.0 HS<br>(Host/Function)                |  |

| 2 x 32 bit GPT<br>x 2 | L1 Cache<br>I-Cache 16 KB                                                                                                           | emory                                                                                | L1 Cache<br>Cache 16 KB                                            | Parallel Bus I/F<br>(up to 32b bus)             |  |

| 1 x WDT per CPU       | D-Cache 16 KB                                                                                                                       |                                                                                      | Cache 16 KB                                                        | Memory Interface                                |  |

| RTC                   |                                                                                                                                     | L2 Cache 256 KB                                                                      |                                                                    |                                                 |  |

| Display               | SRAM 2 MB (with ECC)                                                                                                                |                                                                                      |                                                                    | NAND Flash I/F                                  |  |

| LCD Controller        | R-IN Engine                                                                                                                         |                                                                                      |                                                                    |                                                 |  |

|                       | CPU<br>Arm <sup>®</sup> Cortex <sup>®</sup> -M3                                                                                     |                                                                                      |                                                                    | DDR2/DDR3 I/F                                   |  |

|                       | Arm <sup>-</sup> Cortex <sup>-</sup> M3<br>125 MHz                                                                                  |                                                                                      |                                                                    | 2 x SDIO/eMMC                                   |  |

|                       | MPU D                                                                                                                               | ebug                                                                                 | NVIC                                                               |                                                 |  |

|                       | HW-RTC                                                                                                                              | HW-RTOS Accelerator                                                                  |                                                                    | Analog<br>12bit ADC @1 MHz<br>Up to 2unit × 8ch |  |

|                       | Ethernet Accelerator                                                                                                                |                                                                                      |                                                                    |                                                 |  |

|                       |                                                                                                                                     |                                                                                      |                                                                    |                                                 |  |

|                       | Ethernet                                                                                                                            |                                                                                      |                                                                    |                                                 |  |

|                       | EtherCAT Slave Controller                                                                                                           |                                                                                      |                                                                    |                                                 |  |

|                       | SercosIII Slave Controller                                                                                                          |                                                                                      |                                                                    |                                                 |  |

|                       | Ethernet Switch (4port + 1port)<br>(IEEE1588, QoS, Aging, EEE, Snooping, DLR, TDMA,<br>storm protection, cut-through, Jumbo frames) |                                                                                      |                                                                    |                                                 |  |

|                       | 2x indep                                                                                                                            |                                                                                      |                                                                    |                                                 |  |

|                       | Hardware Redundancy (HSR) Controller                                                                                                |                                                                                      |                                                                    |                                                 |  |

#### CEC CONTINUING EDUCATION CENTER

#### Presented by:

#### **DesignNews**

Blue Ridge Advanced Design and Automation Asheville, North Carolina

# **R-IN Engine Ethernet**

• EtherSwitch (4port + 1port)

– QoS, Aging, EEE, Snooping, DLR, TDMA, Storm protection cut through, Jumbo frames

- Ethernet hardware acceleration

- EtherCAT slave controller

- Sercos<sup>®</sup> III slave controller

- HSR switch (in 400-pin package)

- 5-port Ethernet switch

Question 1– What does storm protection do?

**DesignNews**

## **Energy-Efficient Ethernet**

- IEEE 802.3az

- Establishes a protocol for powering down the PHY transmitter during lulls in transmission

- Significant power savings, less heat dissipation

7

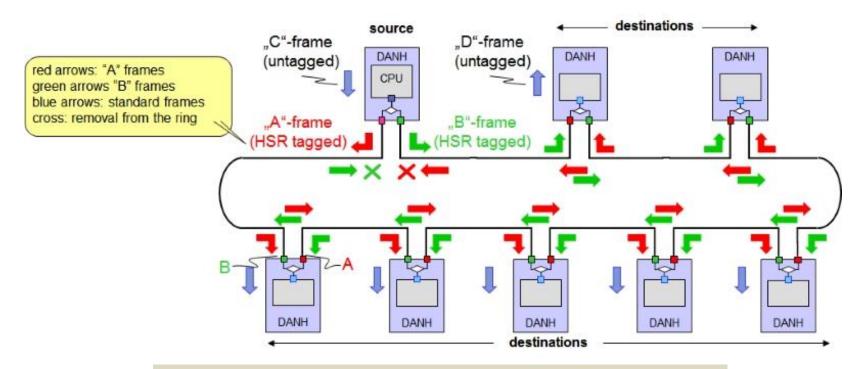

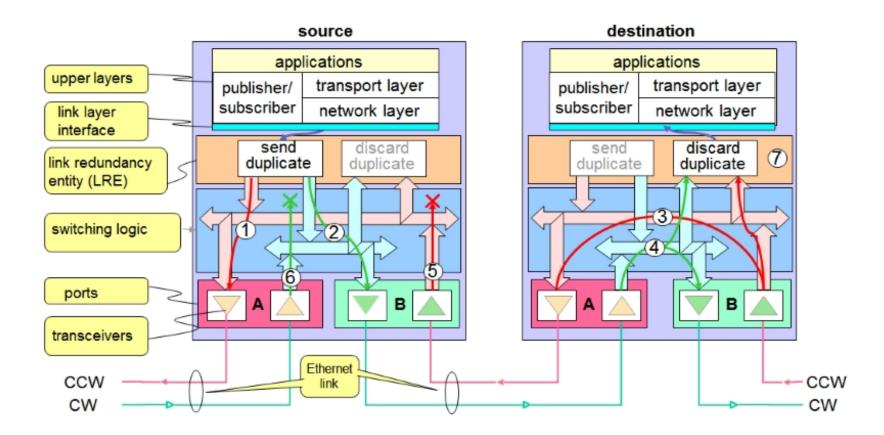

# High-availability Seamless Redundancy (HSR)

HSR is built on a Device Level Ring (DLR) structure

Blue Ridge Advanced Design and Automation Asheville, North Carolina

8

Presented by:

CONTINUING

### **HSR** Detail

Presented by:

CONTINUING EDUCATION

**DesignNews**

Blue Ridge Advanced Design and Automation Asheville, North Carolina

# Other I/O

- UART × 8 channels

- $I^2C \times 2$  channels

- USB Host (HS)

- SPI × 6 channels (4 master, 2 slave)

- CAN bus

- LCD controller

- ADC: 12-bit × 8 channels (2 units in 400pin)

- GPIO and Parallel bus

#### **DesignNews**

10

# **R-IN Communication**

- µITRON-like system calls

- 30 system calls for elements such as events, semaphores, and mailboxes

- Task Scheduler

- Hardware ISR: 32 routines selectable from 128 QINT routines

- Number of context elements: 64

- Number of semaphore identifiers: 128

- Number of event identifiers: 64

- Number of mailbox identifiers: 64

- Number of mailbox elements: 192

- Number of context priority levels: 16

Question 2 – What is the difference between ITRON and µITRON?

Presented by:

#### Blue Ridge Advanced Design and Automation Asheville, North Carolina

### Example - PLC

Blue Ridge Advanced Design and Automation Asheville, North Carolina 12

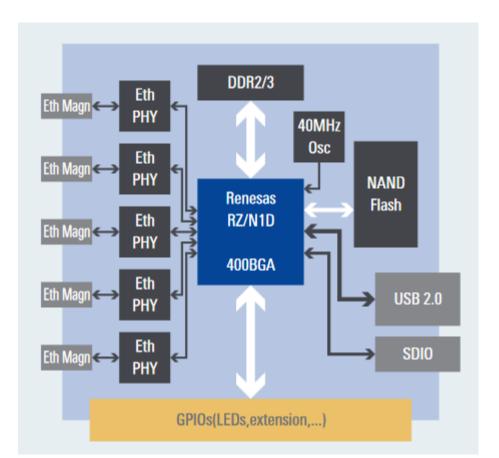

### RZ/N1 Boards

#### Dual Cortex-A7

**RZ/N1D CPU Board**

#### Single Cortex-A7

**RZ/N1S CPU Board**

#### **R-IN Engine**

**RZ/N1L CPU Board**

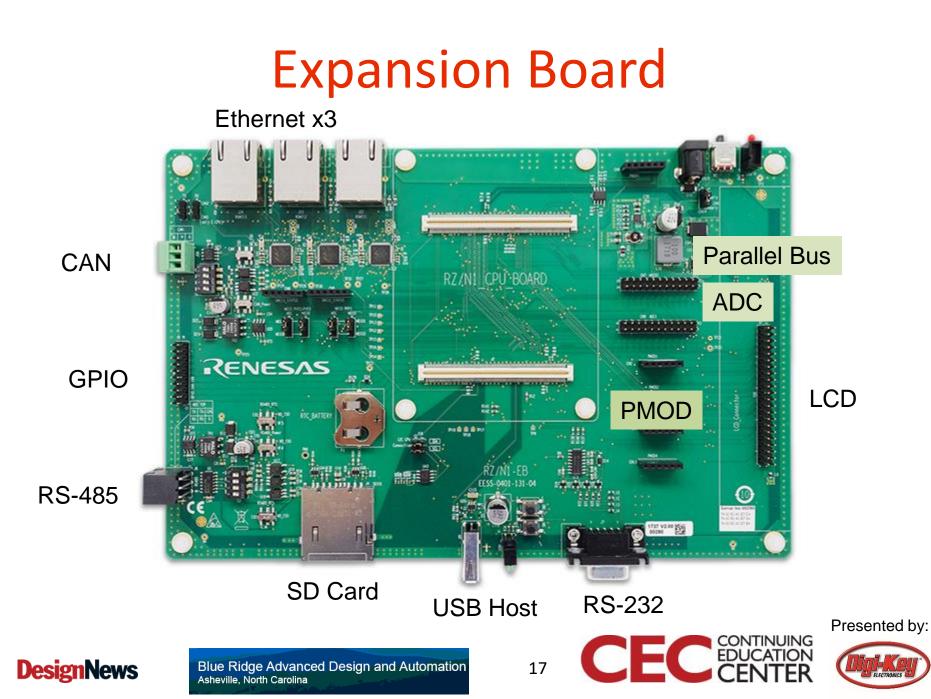

#### Expansion Board

Q

**RZ/N1 Expansion Board**

#### **DesignNews**

Blue Ridge Advanced Design and Automation Asheville, North Carolina

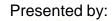

### Example – Hub or Gateway

#### Note – single Cortex A7 Processor

Application example: Sensor Hub block diagram

Blue Ridge Advanced Design and Automation Asheville, North Carolina 14

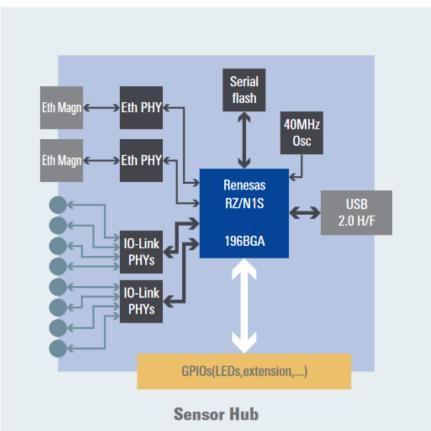

# RZ/N1L (R-IN Stand Alone)

#### RZ/N1L block diagram

Blue Ridge Advanced Design and Automation Asheville, North Carolina 15

### **Development Board**

- Basic CONNECT-IT! Kit

- RZ/N1D Board

- IAR I-jet Lite JTAG

- DVD with software, manuals

- Cables

16

Available for loan from your Renesas office

#### **DesignNews**

Blue Ridge Advanced Design and Automation Asheville, North Carolina CEC

# Developing With the RZ/N1D

- Treat as two entities:

- Application Processor (Dual ARM Cortex-A7)

- Communications Processor (ARM Cortex-M3)

- Application Processor can either be programmed with an RTOS or with a full O/S (Linux – preferred)

- Communications processor is programmed with an RTOS

- Code is provided for both Linux (including a port) and baremetal / RTOS

- More on this Thursday and Friday!

Presented by:

#### **DesignNews**

### **Industrial Ethernet Stacks**

#### **RZ/N Series: Solutions from Renesas Partners**

A variety of software solutions are available from vendors with deep expertise in industrial networks.

| Protocol Vendor                               |                                                                                          |  |  |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|

| Port.GmbH                                     | Industrial network stack<br>PROFINET (Slave)<br>EtherNet/IP (Slave)<br>Powerlink (Slave) |  |  |  |

| TMG<br>(TMG Technologie und Engineering GmbH) | Industrial network stack<br>PROFINET (Slave)<br>EtherNet/IP (Slave)                      |  |  |  |

| Cannon Automata                               | Industrial network stack<br>Sercos® III (Slave)                                          |  |  |  |

| NetModule                                     | Redundant protocol<br>HSR/PRP                                                            |  |  |  |

#### **DesignNews**

19

### **Available Development Environments**

#### **RZ/N Series: Development Environments**

**DesignNews**

|          | <b>SYSTEMS</b>                                      |                                                         | RENESAS                  |

|----------|-----------------------------------------------------|---------------------------------------------------------|--------------------------|

| CPU Core | Cortex <sup>®</sup> -A7     Cortex <sup>®</sup> -M3 | <ul> <li>Cortex<sup>®</sup>-A7 (for VxWorks)</li> </ul> | • Cortex®-A7 (for Linux) |

| Debugger | <ul> <li>Embedded</li> <li>Workbench</li> </ul>     | Eclipse                                                 | • GDB                    |

| Compiler | • IAR<br>• C/C++Compiler                            | • GCC<br>• DIAB                                         | • GCC                    |

| ICEs     | ● I-jet™                                            | • JTAG debugger (LAUTERBACH)                            | • J-Link (SEGGER)        |

Question 3 – What popular board uses Cortex A7 cores (and typically Linux)?

Presented by:

CONTINUING

## **Common Abstraction**

- Programming our ports to accommodate all of these protocols needs a common abstraction layer

- The Renensas RZ/N1D R-IN protocol engine makes use of the GOAL (Generic Open Abstraction Layer) from PORT GmbH in order to make our programming more straightforward

- More on this tomorrow!

**DesignNews**

21

# This Week's Agenda

- 10/22 The Challenges of IIoT and Industrial Ethernet

- 10/23 Introduction to the RZ/N1

- 10/24 Many Protocols, One Abstraction GOAL

- 10/25 Programming the R-IN Protocol Engine

- 10/26 Writing and Testing Our Application

# Please stick around as I answer your questions!

- Please give me a moment to scroll back through the chat window to find your questions

- I will stay on chat as long as it takes to answer!

- I am available to answer simple questions or to consult (or offer in-house training for your company) c.j.lord@ieee.org http://www.blueridgetechnc.com http://www.blueridgetechnc.com

http://www.linkedin.com/in/charleslord

Twitter: @charleslord

https://www.github.com/bradatraining

Presented by:

**DesignNews**