# DesignNews

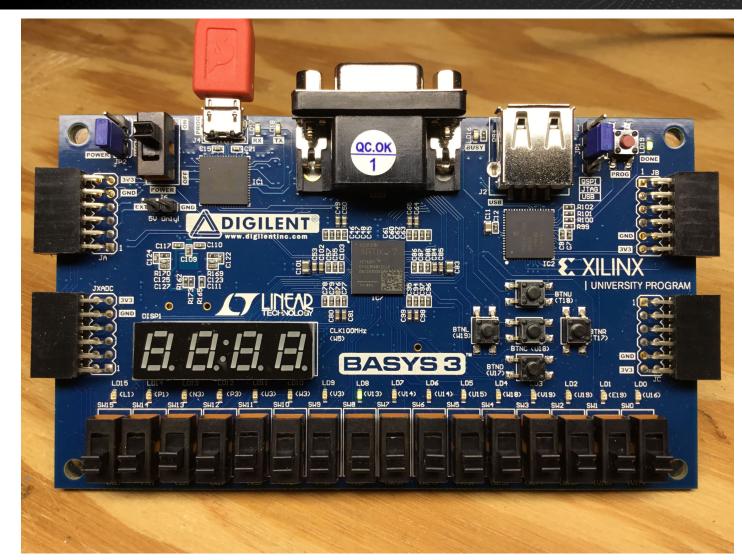

Field-Programmable Gate Array (FPGA) Primer

**Day 5:**

Hardware and Software Design with Vivado and Vitis

Sponsored by

## Webinar Logistics

- Turn on your system sound to hear the streaming presentation.

- If you have technical problems, click "Help" or submit a question asking for assistance.

- Participate in 'Attendee Chat' by maximizing the chat widget in your dock.

Fred Eady

Visit 'Lecturer Profile' in your console for more details.

## AGENDA

- Create a Block Design with Vivado

- Finish the Design with Vitis

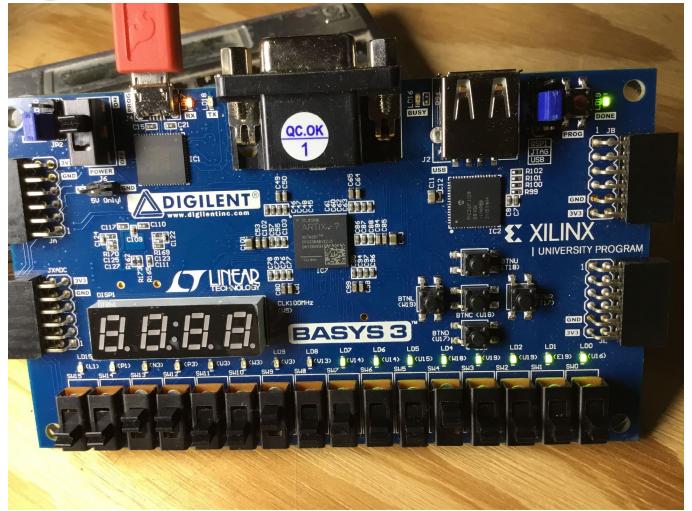

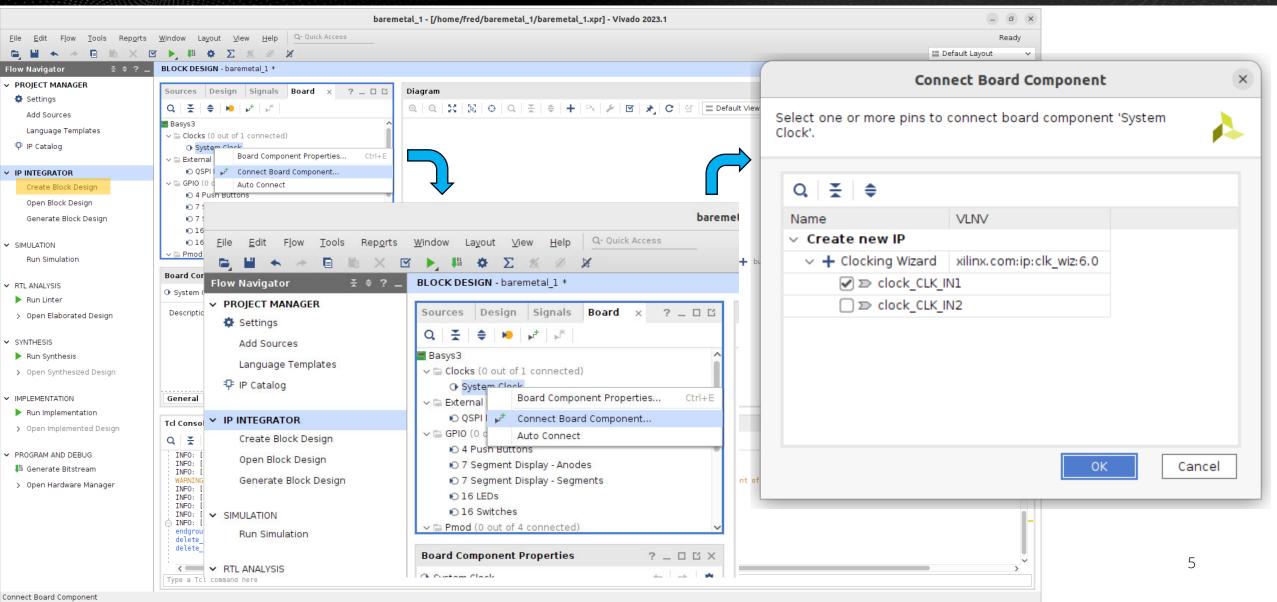

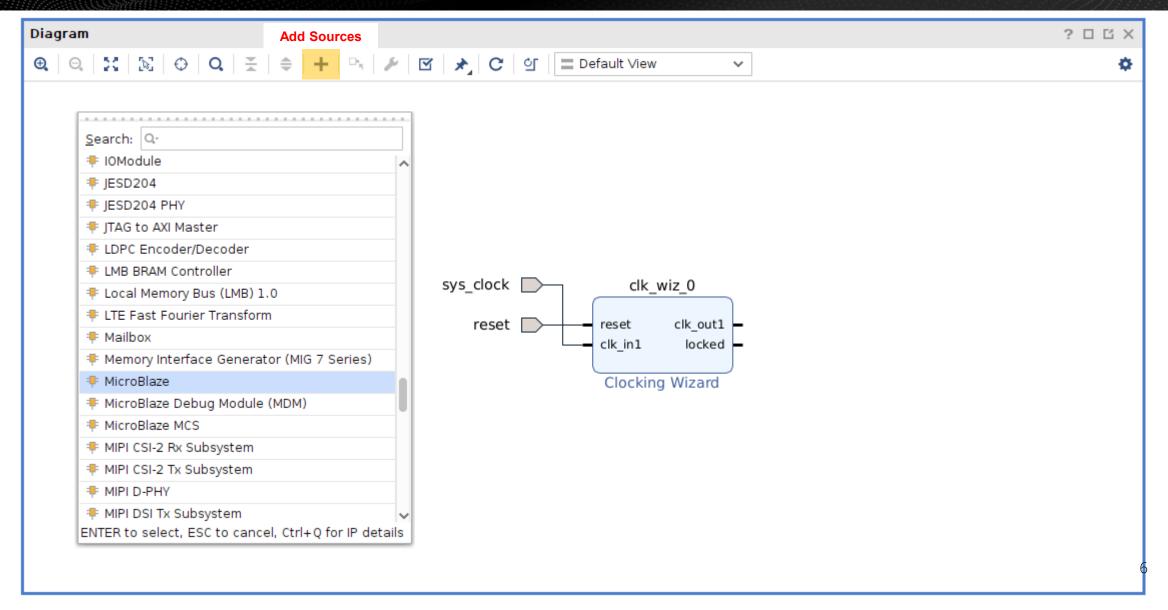

### **Create Block Design and Add System Clock**

Sponsored By

#### **Add MicroBlaze**

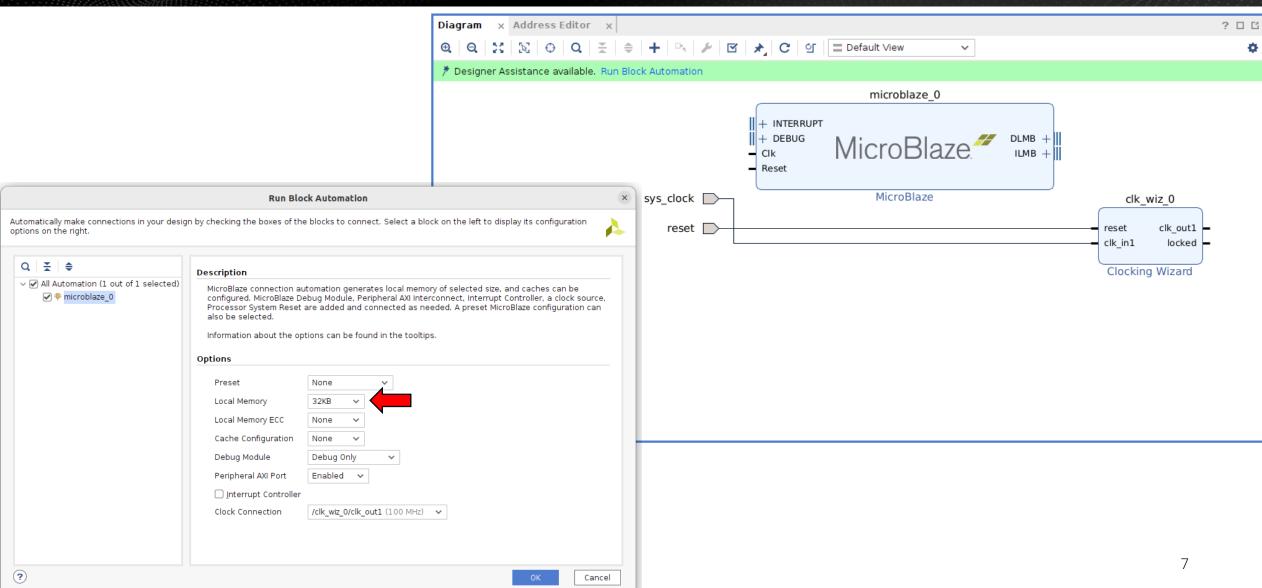

### **Specify 32KB of Local Memory**

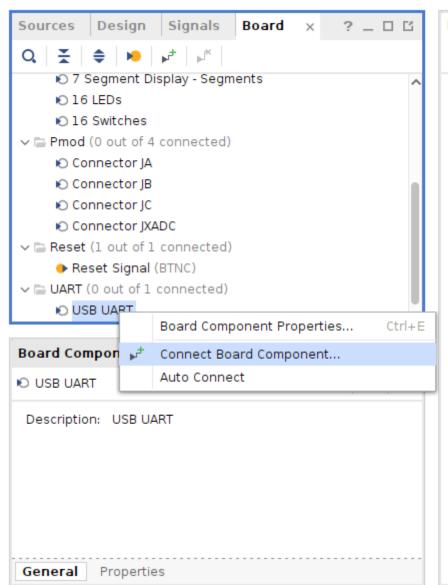

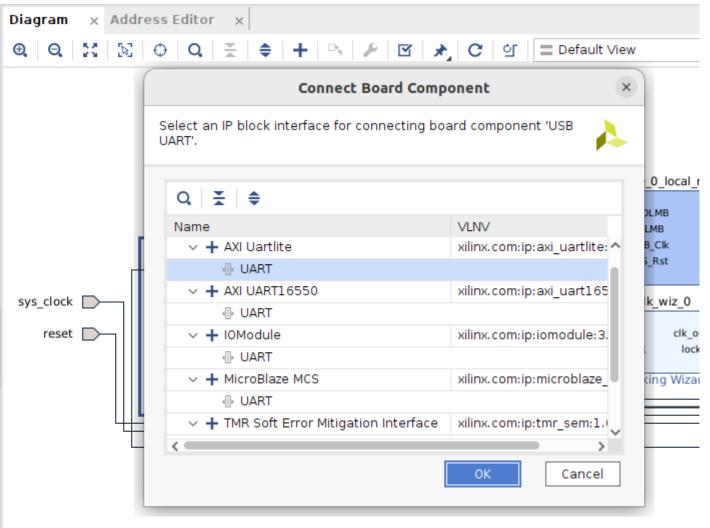

#### **Add USB UART**

Sponsored By

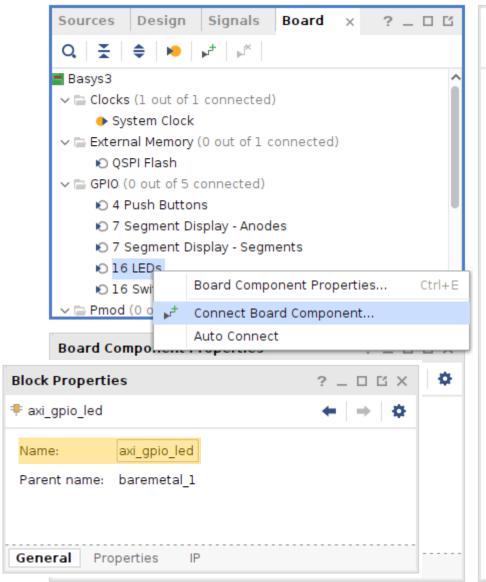

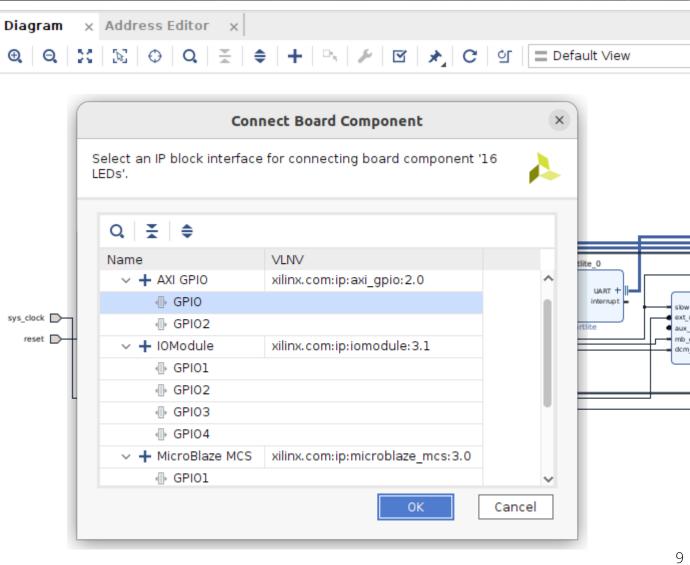

#### **Add Bank of 16 LEDs — Rename LED Block**

Sponsored By

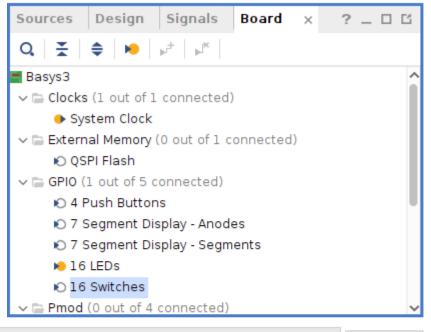

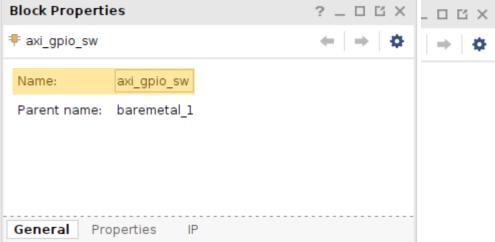

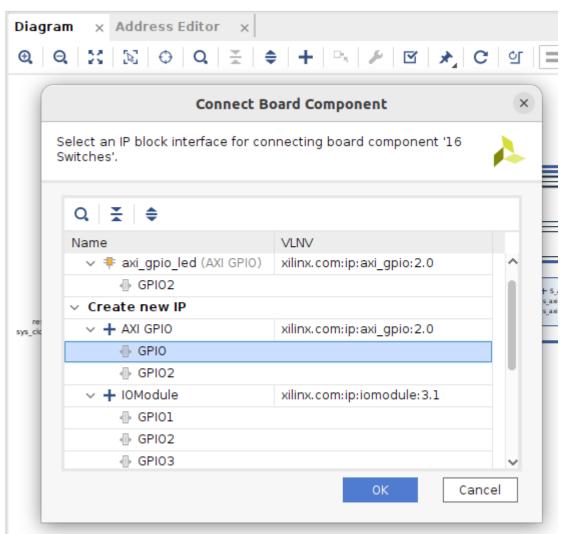

#### **Add Bank of 16 Switches – Rename Switch Block**

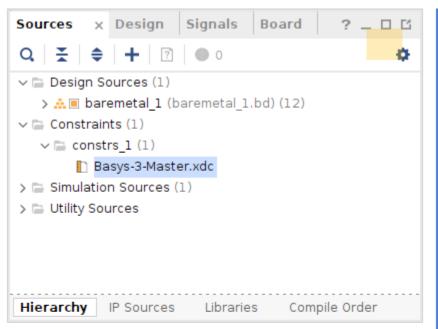

### **Add Basys 3 Constraint File**

```

Diagram x Address Editor x

Basys-3-Master.xdc *

/home/fred/baremetal 1/Basys-3-Master.xdc

♠ | → | 从 | □ | □ | X | // | Ⅲ | ♀

6 ## Clock signal

create clock -add -name sys clk pin -period 10.00 -waveform {0 5} [get ports clk]

10 : ## LEDs

IOSTANDARD LVCMOS33 } [get ports {led[5]}]

16 : set property -dict { PACKAGE PIN U15

17 ; set property -dict { PACKAGE PIN Ul4

IOSTANDARD LVCMOS33 } [get ports {led[6]}]

IOSTANDARD LVCMOS33 } [get_ports {led[7]}]

18 | set property -dict { PACKAGE PIN V14

19 | set property -dict { PACKAGE PIN V13

IOSTANDARD LVCMOS33 } [get ports {led[8]}]

IOSTANDARD LVCMOS33 } [get ports {led[9]}]

20 set property -dict { PACKAGE PIN V3

IOSTANDARD LVCMOS33 } [get ports {led[10]}]

21 set property -dict { PACKAGE PIN W3

IOSTANDARD LVCMOS33 } [get ports {led[11]}]

22 set property -dict { PACKAGE PIN U3

IOSTANDARD LVCMOS33 } [get ports {led[12]}]

23 ; set property -dict { PACKAGE PIN P3

IOSTANDARD LVCMOS33 } [get ports {led[13]}]

24 | set property -dict { PACKAGE PIN N3

IOSTANDARD LVCMOS33 } [get ports {led[14]}]

25 | set property -dict { PACKAGE PIN Pl

IOSTANDARD LVCMOS33 } [get ports {led[15]}]

26 | set property -dict { PACKAGE PIN L1

27

28

29 : ##7 Segment Display

30 | #set_property -dict { PACKAGE_PIN_W7 | IOSTANDARD_LVCMOS33 } [get_ports {seg[0]}]

31 | #set property -dict { PACKAGE PIN W6 IOSTANDARD LVCMOS33 } [get ports {seg[1]}]

32 | #set property -dict { PACKAGE PIN U8 | IOSTANDARD LVCMOS33 } [get ports {seg[2]}]

33 #set property -dict { PACKAGE PIN V8 IOSTANDARD LVCMOS33 } [get ports {seg[3]}]

34 #set property -dict { PACKAGE PIN U5

IOSTANDARD LVCMOS33 } [get ports {seg[4]}]

IOSTANDARD LVCMOS33 } [get ports {seg[5]}]

35 #set_property -dict { PACKAGE_PIN V5

36 #set property -dict { PACKAGE PIN 117

TOSTANDARD I VCMOS33 } [net norts {sen[6]}]

```

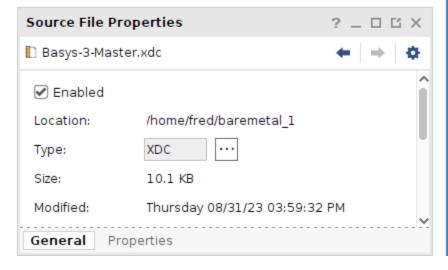

### **Validate the Design**

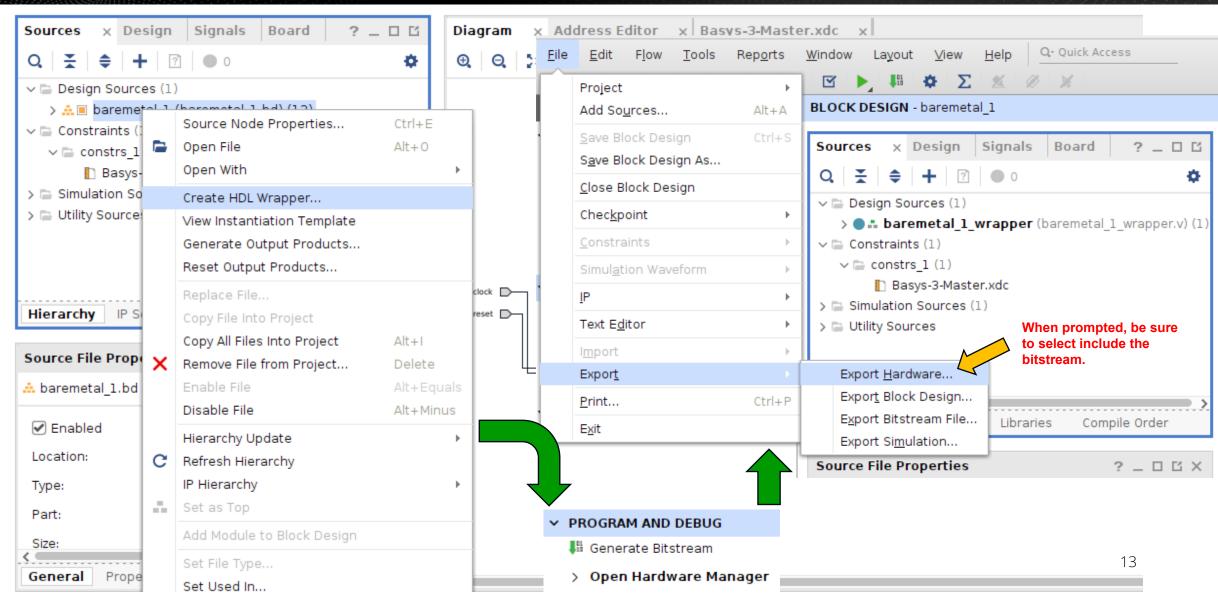

### **Create the HDL Wrapper – Generate Bitstream - Export**

Sponsored By

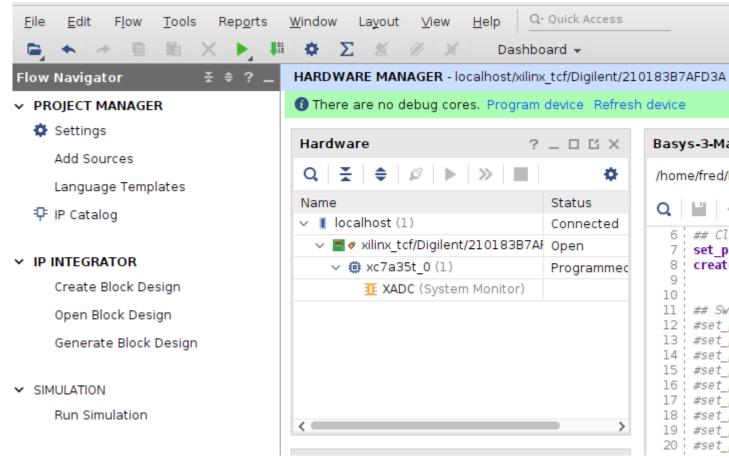

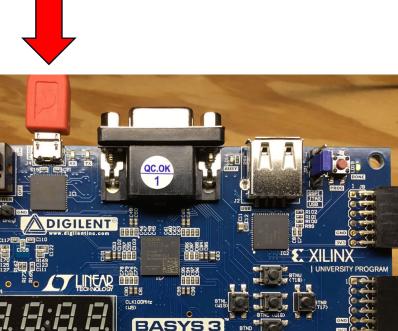

### **Activate Hardware Manager**

9

12

10

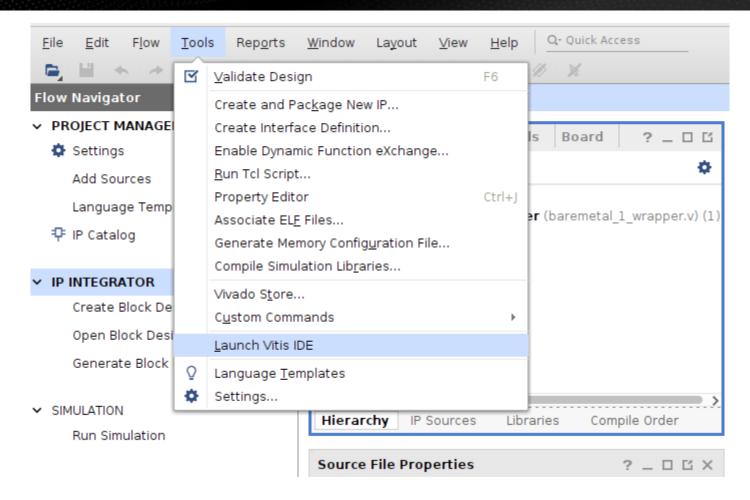

#### **Enter... Vitis**

Field-Programmable Gate Array (FPGA) Primer

Hardware and Software Design with Vivado and Vitis

Finish the Design with Vitis

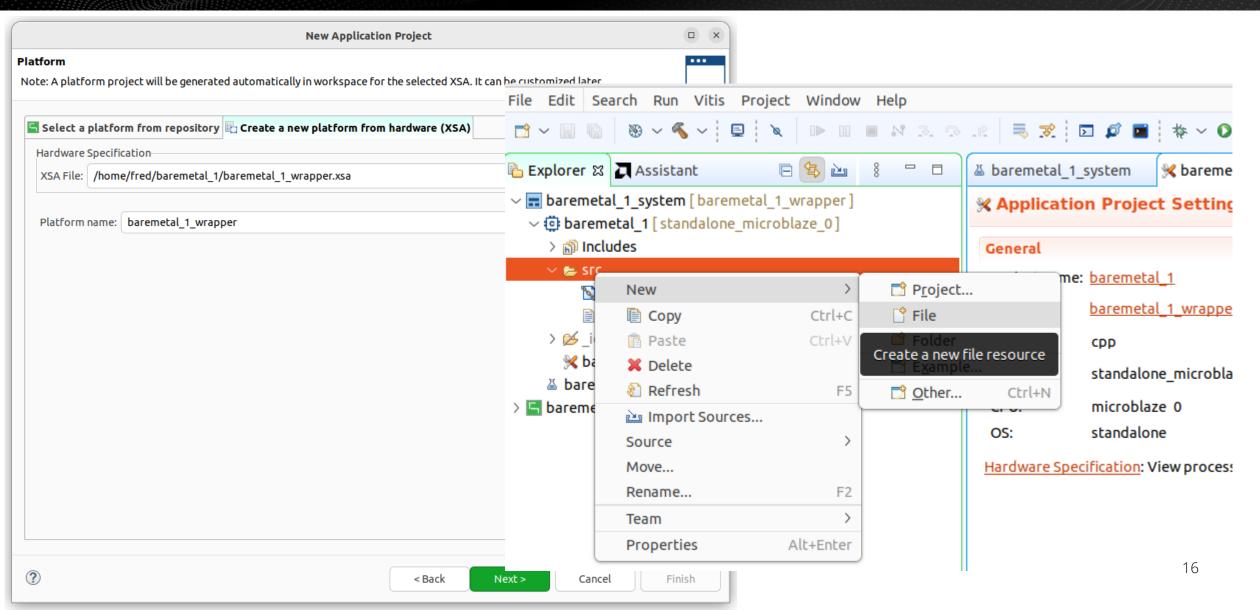

#### **Create main.c**

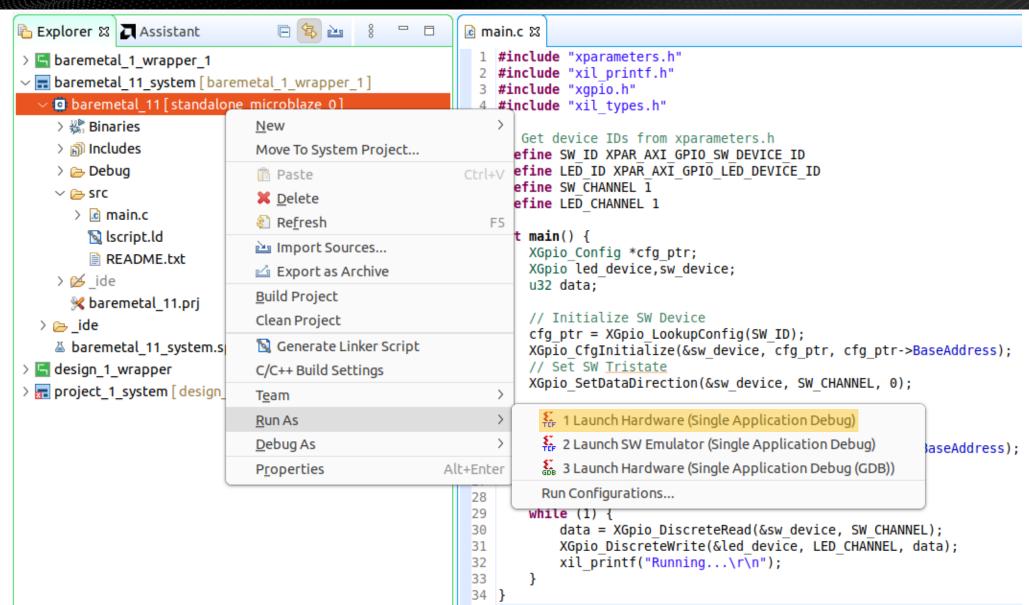

### **Vitis Application Code**

```

_ _

1 #include "xparameters.h"

2 #include "xil printf.h"

3 #include "xqpio.h"

4 #include "xil types.h"

6 // Get device IDs from xparameters.h

7 #define SW ID XPAR AXI GPIO SW DEVICE ID

8 #define LED ID XPAR AXI GPIO LED DEVICE ID

9 #define SW CHANNEL 1

10 #define LED CHANNEL 1

11

12⊖ int main() {

XGpio Config *cfg ptr;

13

14

XGpio led device, sw device;

15

u32 data;

16

17

// Initialize SW Device

18

cfg ptr = XGpio LookupConfig(SW ID);

XGpio CfgInitialize(&sw device, cfg ptr, cfg ptr->BaseAddress);

19

20

// Set SW Tristate

21

XGpio SetDataDirection(&sw device, SW CHANNEL, 0);

22

23

// Initialize LED Device

24

cfg ptr = XGpio LookupConfig(LED ID);

25

XGpio CfgInitialize(&led device, cfg ptr, cfg ptr->BaseAddress);

26

// Set Led Tristate

27

XGpio SetDataDirection(&led device, LED CHANNEL, 0);

28

29

while (1) {

data = XGpio DiscreteRead(&sw device, SW CHANNEL);

30

31

XGpio DiscreteWrite(&led device, LED CHANNEL, data);

32

xil printf("Running...\r\n");

33

34 }

```

#### Run it

# Field-Programmable Gate Array (FPGA) Primer Hardware and Software Design with Vivado and Vitis Finish the Design with Vitis

Sponsored By

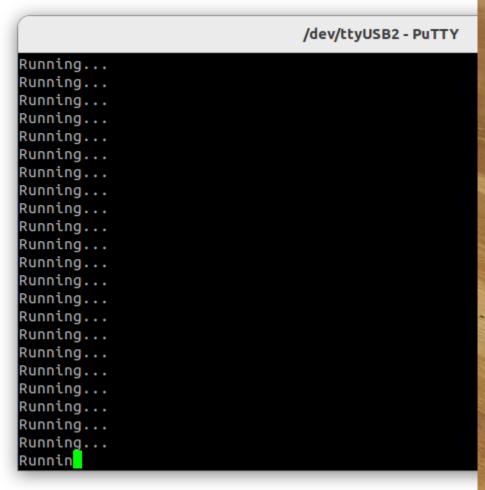

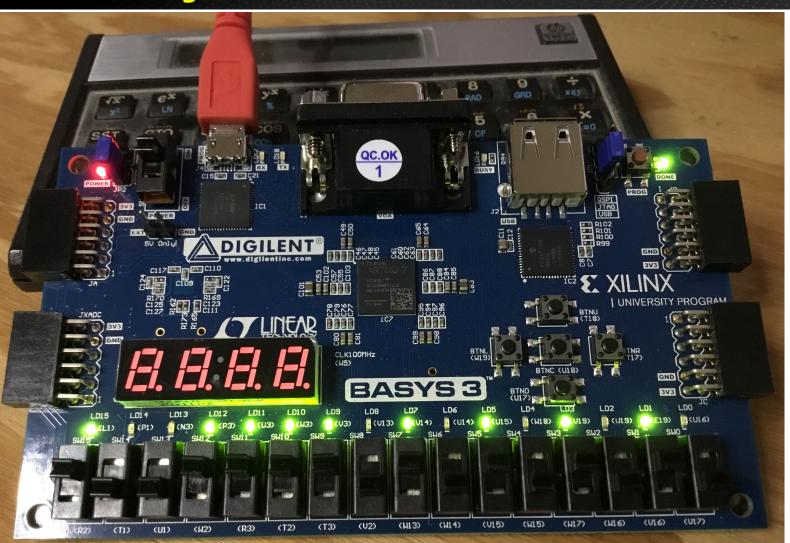

### **Running...**

## Thank you for attending!!!

#### Please consider the resources below:

- xilinx.com

- digilent.com

- Basys 3 Reference Manual

# DesignNews

# Thank You

Sponsored by