# **FPGA Programming**

Class 4: Synthesis and Layout

September 14, 2017 Louis W. Giokas

# This Week's Agenda

Monday FPGA Device Description

Tuesday Design Flow

Wednesday HDL

Thursday Synthesis and Layout

Friday Programming the Chip

## **Course Description**

We start with an introduction to the class of devices called Field Programmable Gate Arrays (FPGAs). The layout and design of several types and critical parameters will be described and discussed. It is important to understand the way the device is constructed to develop effective algorithms.

The device we will be using this week will be the Microsemi IGLOO2. We will also discuss other devices and their structure.

We will introduce two common Hardware Description Languages (HDL), but give examples in one (Verilog).

# Today's Agenda

- Process Overview

- Software Tools

- Synthesis

- Layout

- Conclusion/Next Class

### **Process Overview**

- In a typical FPGA design flow, comes after the design has been created and verified and constraints have been defined

- Examples will be given using tools from Microsemi

- Main tool is Libero

- We are using the latest version (11.8)

## **Process Overview**

Create Design Pre-Compile Constraint Editor - I/O Constraint and Floorplan Constraint Create Constraints files are separated - Enables you to import Timing Constraint (SDC) files Pre-Conpile Synthesis We are concentrating on these tasks Post-Compile I/O Editor Compile - Assign pins and attributes - Check rules State Management on Modifications Place-and-Route Post-Compile PDC file - Post-Compile I/O PDC file generated automatically if you explicitly add/modify your Program Design I/O Constraints Post-Compile - Generate Bitstream - Run Program Action - Option 1 Option 2 **Handoff Design for Production** FlashPro/FlashPro Express - Export Bitstream - Export Programming Job All other Programming Methods

## **Process Overview**

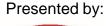

In Libero it looks like this. We will review these items.

## **Software Tools**

- Generally vendors provide a suite of tools to develop algorithms for FPGAs

- Xilinx: Vivado

- Intel: Quartus

- Microsemi: Libero

- Tool suites are expensive (several thousand \$)

- Generally include third party simulation and place and route

- Not an area where open source tool chains are generally effective

## **Software Tools**

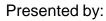

### Simulation tools:

- ModelSim by Mentor Graphics is the most popular modeling and simulation tool

- Generally included with a license tied to the particular device

### Layout tools:

- Synplify by Synopsis is one of the more popular tools for the synthesis and layout task

- Others can be used, in some cases not integrated

## **Software Tools**

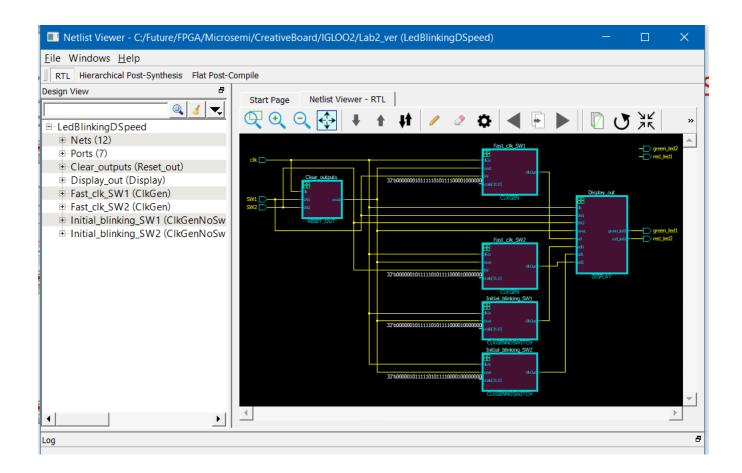

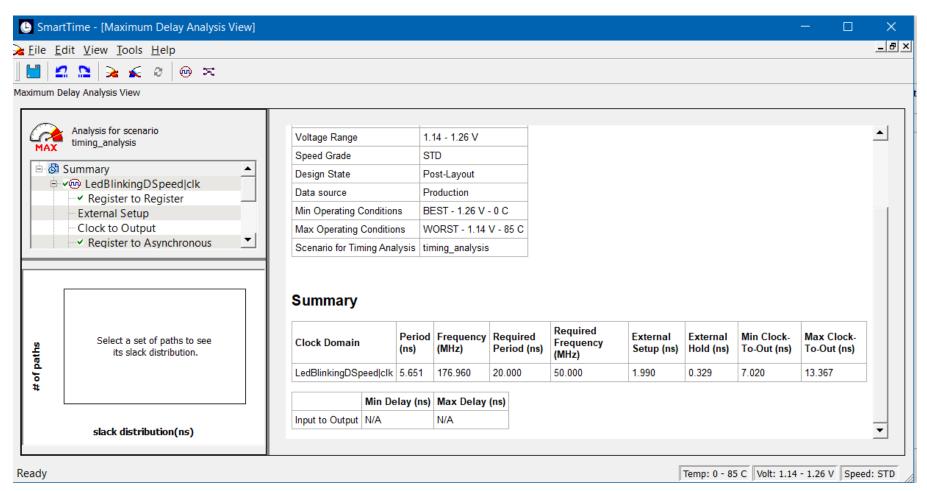

- The development environments also have a number of tools, that often run in different windows, to perform functions unique to the FPGA (showing Libero application names)

- Netlist viewer: can show RTL generated

- SmartTime: max, min and bottleneck analysis

- Power reports (inside Libero): shows power down to the module level

- Synthesis takes our VHDL design and produces

RTL

- We will use a couple of simple applications to illustrate the tools and processes of synthesis

- One will be a simple application to blink lights on the board

- One uses the access to memory to observe the design process

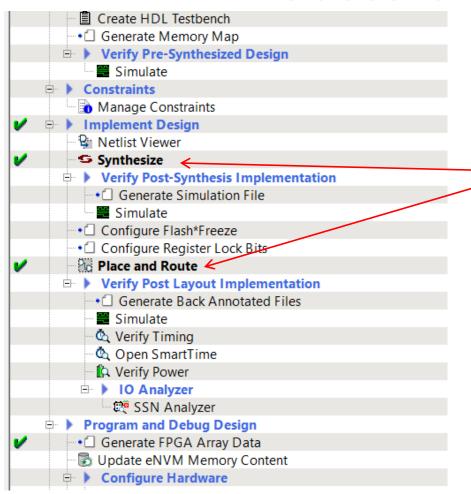

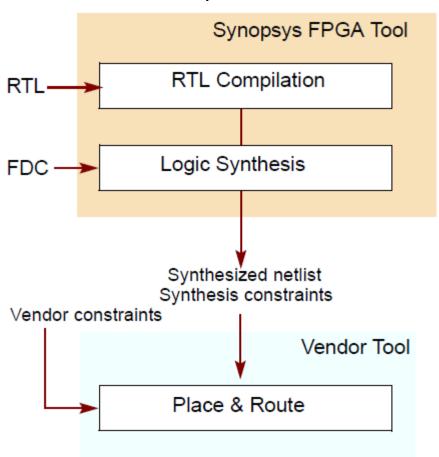

### Process

- RTL first translated into a technology independent logic structures

- Next these technology independent structures are mapped and optimized for the particular technology being used

- Output is a vendor-specific netlist and constraint file that is input to the place and route tool

### Tool Relationship

### **Process Flow**

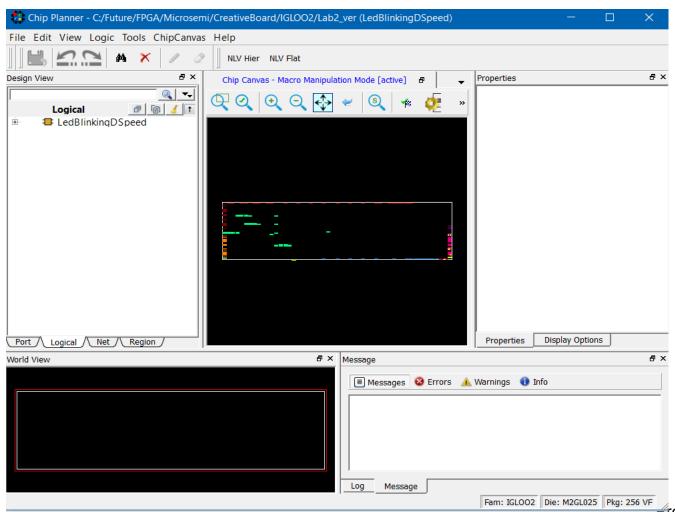

Netlist for a simple program that blinks lights in the board

- Layout is also referred to as place and route

- The first process of deciding where on the chip to put each circuit element

- Next the interconnections and pathways are determined

- This process is iterated until a design that implements the constraints is achieved

- Some of the major considerations in this step are timing and power usage

- Tools are provided to view, in great detail, the timing and power usage of each component of the design

- Tied back to the labels used in the HDL

- After the HDL, constraints are the most important input

- It is the combination of our design and the constraints that make place and route work

Presented by:

17

#### Power Report for design LedBlinkingDSpeed with the following settings:

| Vendor:  | Microsemi Corporation                                                       |  |  |

|----------|-----------------------------------------------------------------------------|--|--|

| Program: | Microsemi Libero Software, Release Libero SoC v11.8 SP1 (Version 11.8.1.12) |  |  |

|          | Copyright (C) 1989-                                                         |  |  |

| Date:    | Thu Sep 14 08:35:20 2017                                                    |  |  |

| Version: | 3.0                                                                         |  |  |

| Design:               | LedBlinkingDSpeed |  |

|-----------------------|-------------------|--|

| Family:               | IGLOO2            |  |

| Die:                  | M2GL025           |  |

| Package:              | 256 VF            |  |

| Temperature Range:    | COM               |  |

| Voltage Range:        | COM               |  |

| Operating Conditions: | Typical           |  |

| Operating Mode:       | Active            |  |

| Process:              | Typical           |  |

| Data Source:          | Production        |  |

#### **Power Summary**

|               | Power (mW) | Percentage |

|---------------|------------|------------|

| Total Power   | 20.048     | 100.0%     |

| Static Power  | 13.850     | 69.1%      |

| Dynamic Power | 6.198      | 30.9%      |

The system generates power reports with enough detail for the engineer to determine where power is being used, overall level and identify potential trouble spots.

As a part of the constraint process we can designate parts of the chip to be empty (so we can put a new element later) or where we want to place active elements.

# Conclusion/Next Class

- Today we looked at two more steps in the FPGA design flow

- Synthesis: design/algorithms to RTL

- Layout: placing the synthesized design on the FPGA

- Examples from the Microsemi tool chain were used

- Other vendors' tool chains are similar and often used the same third party tools

- Tomorrow we will get into the programming and debug processes