# **FPGA Programming**

Class 3: HDL

September 13, 2017 Louis W. Giokas

# This Week's Agenda

Monday FPGA Device Description

Tuesday Design Flow

Wednesday HDL

Thursday Synthesis and Layout

Friday Programming the Chip

### **Course Description**

We start with an introduction to the class of devices called Field Programmable Gate Arrays (FPGAs). The layout and design of several types and critical parameters will be described and discussed. It is important to understand the way the device is constructed to develop effective algorithms.

The device we will be using this week will be the Microsemi IGLOO2. We will also discuss other devices and their structure.

We will introduce two common Hardware Description Languages (HDL), but give examples in one (Verilog).

# Today's Agenda

- Overview

- Tutorial

- Examples

- Conclusion/Next Class

- A Hardware Description Language (HDL) is used to provide a precise description of the structure and behavior of electronic circuits in a textual form

- We use HDL to describe the functions to be implemented in the FPGA

- We also use it to describe all the control lines required by our application

- HDL History

- First modern HDL was Verilog (mid-1980s)

- VHDL was introduced by the US Department of Defense (DoD) in the late 1980s. It is based on the Ada language

- Other HDLs existed, but these are the two used today

- Example: System-C

- System Verilog is used for verification

- It is an extension of Verilog

- HDL Standards

- HDLs in use have been made into IEEE standards

- Verilog: IEEE 1364-2005

- System Verilog: IEEE 1800-2012

- VHDL: IEEE 1076-2008

- Standardization ensures that code can be processed by compilers from multiple vendors

- Also allows code developed separately to be combined

- The reason for the use of HDLs is that circuits began to get so complex that creating and maintaining circuit diagrams became too difficult

- Using concepts from computer engineering concepts such as layering and data hiding increased the size of circuitry that could be specified

- Still a complex process, but with good tools, manageable

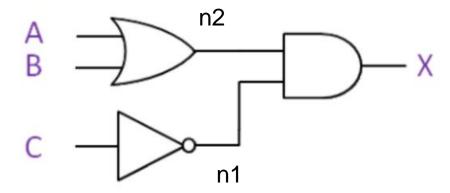

- We will go over a simple circuit that combines a few types of gates just to get the idea

- This is not a comprehensive example or tutorial, just an introduction

- Just want to highlight some of the syntax

- Out little example could be used a door opener

- The Verilog language allow the specification of logic elements and the connections between them

- We specify inputs and outputs

- We specify wires within the circuit

- We specify structure of the circuit

- We specify behavior of the circuit elements and overall circuit

```

Emodule Inv(x, F);

input x;

output F;

// details not shown

Lendmodule

\square module OR2 (x, y, F);

input x, y;

output F;

reg F;

always @ (x or y)

begin

F \ll x \mid y;

end;

Lendmodule;

\square module AND2(x, y, F);

input x, y;

output F;

// details not shown

Lendmodule:

⊟module Circuit1 ( A, B, C, X );

input A, B, C;

output X;

wire n1, n2;

Inv Inv 1 ( C, n1 );

OR2 OR2 1 ( A, B, n2 );

AND2 AND2 1 ( n1, n2, X);

endmodule;

```

```

Behavior

Behavior

Imput A, B, C;

output X;

reg X;

always @ ( A or B or C)

begin

X <= (-A) & ( B | C );

end

endmodule;

```

Structure

- Notice that we define the primitive circuit types and their behaviors as types

- Generally these will be in a library

- We then instantiate them, possibly many times

- We also have to define all the signals, inputs and wires as types, then we use them in the structural description

- Built in types, such as wire, are available

- In the following we will go through several code snippets

- The first couple will be complete routines

- Then we will look at code from a FFT implementation

- The goal is to show the power, as well as the complexity

- Code is color coded, showing keywords and user defined symbols

```

`timescale 1ns / 1ns

module counter (count, clk, reset);

output [7:0] count;

input clk, reset;

reg [7:0] count;

parameter tpd reset to count = 3;

parameter tpd clk to count = 2;

function [7:0] increment;

input [7:0] val;

reg [3:0] i;

reg carry;

begin

increment = val;

carry = 1'b1;

* Exit this loop when carry == zero, OR all bits processed

for (i = 4'b0; ((carry == 4'b1) && (i <= 7)); i = i + 4'b1)

increment[i] = val[i] ^ carry;

carry = val[i] & carry;

end

end

endfunction

always @ (posedge clk or posedge reset)

if (reset)

count = #tpd reset to count 8'h00;

count <= #tpd clk to count increment(count);</pre>

endmodule

```

A simple counter. Note the multibit entities.

```

wire qval;

reg dval;

reg clear;

reg preset;

reg clock;

dff dff_inst( qval, dval, clear, preset, clock );

reg control, din;

wire udp_out;

sudp sudp_inst( udp_out, control, din );

wire muxout;

reg ctl, dA, dB;

multiplexer mult_inst( muxout, ctl, dA, dB );

endmodule

```

Shows use of clock signals. Below is the behavior of the dff type used in the main module.

```

`timescale 1ns / 1ps

`celldefine

module dff (q, d, clear, preset, clock);

output q;

input d, clear, preset, clock;

req q;

always @(clear or preset)

if (!clear)

assign q = 0;

else if (!preset)

assign q = 1;

deassign q;

always @(posedge clock)

a = d;

endmodule

`endcelldefine

```

```

module fft 32K (

clk,

reset,

master_sink_dav,

master sink sop,

master source dav,

inv_i,

data real in.

data imaq in,

fft real out.

fft_imag_out,

exponent out,

master_sink_ena,

master source sop.

master source eop,

master_source_ena);

// GLOBAL PARAMETER DECLARATION

parameter data_width = 16; //The number of bits in the input data for both real and imag parts

parameter twiddle width = 16; //The number of bits in the twiddle factor for both real and imag parts

parameter transform_length = 32768;

parameter coshex init file = "fft 32K coshex.hex";

parameter sinhex init file = "fft 32K sinhex.hex";

parameter log2 transform length = 15;

parameter

mram buf add width = 15;

input

clk;

reset;

input

input

master sink dav;

input

master sink sop;

input

master source dav;

input

inv i;

input

[data width-1:0]

data real in:

input

[data width-1:8]

data imaq in;

[data width-1:0]

fft real out;

output

[data_width-1:0]

fft_imag_out;

output

[5:0] exponent out;

output

output

master sink ena;

output

master source sop;

output

master source eop;

output

master source ena;

wire

clk fft;

wire

clk data;

[data_width-1:0] data_real_in_fft_top;

wire

[data width-1:0]

wire

data imaq in fft top;

wire

[data width-1:0] data real in fft bot;

wire

[data width-1:0] data imag in fft bot;

wire

inv i fft;

wire

master sink ena comb;

master sink ena fft top;

wire

wire

master_sink_ena_fft_bot;

wire

master sink dav fft;

wire

master_sink_sop_fft;

```

This is the beginning of a FFT module. I know it is hard to read, but I wanted to give you an idea of the amount of detail required.

```

always @ (posedge clk data out)

begin

if(reset == 1'b1)

begin

tf sp d1 <= 1'b0;

tf sp d2 <= 1'b0;

cnt dir d1 <= 1'b0;

cnt dir d2 <= 1'b0;

count reg <= 0;

end

else

begin

tf sp d1 <= reset cnt;

tf sp d2 <= tf sp d1;

cnt dir d1 <= cnt dir;

cnt dir d2 <= cnt dir d1;

count reg <= count;

end

end

always @ (posedge clk fft)

begin

if (reset == 1'b1)

cnt en d1 \ll 0;

else

cnt_en_d1 <= cnt_en;</pre>

end

```

In this code snippet we are manipulating the bits of the real and imaginary parts. Note that there is lots of definition of signals preceding this.

```

always @ (posedge clk fft)

begin

if (reset == 1'b1)

real top d1 <= 0;

imag top d1 \ll 0;

real top d2 <= 0;

imag top d2 <= 0;

real top d3 <= 0;

imag top d3 <= 0;

real top d4 <= 0;

imag top d4 \ll 0;

real top d5 <= 0;

imag top d5 \ll 0;

master source sop reg <= 1'b0;

master source ena reg <= 1'b0;

master source ena reg1 <= 1'b0;

master source ena reg2 <= 1'b0;

master source ena reg3 <= 1'b0;

master source ena reg4 <= 1'b0;

master source ena reg5 <= 1'b0;

mram rden d1 <= 1'b0;

end

else

real top d1 <= {sign real, sign real, fft real out fft top};</pre>

imag top d1 <= {sign imag, sign imag, fft imag out fft top};</pre>

real top d2 <= real top d1;

imag top d2 <= imag top d1;

real top d3 <= real top d2;

imag top d3 <= imag top d2;

real top d4 <= real top d3;

imag top d4 <= imag top d3;

real top d5 <= real top d4;

imag top d5 <= imag top d4;

master source sop reg <= master source sop;

master source ena reg <= master source ena;

master source ena reg1 <= master source ena reg;

master source ena reg2 <= master source ena reg1;

master source ena reg3 <= master source ena reg2;

master source ena reg4 <= master source ena reg3;

master source ena reg5 <= master source ena reg4;

mram rden d1 <= mram rden;

end

end

```

In this module we are combining the final results

```

always @ (posedge clk data out)

begin

if (reset == 1'b1)

begin

rr scaled shifted d1 <= 0;

ri scaled shifted d1 <= 0;

rr scaled shifted d2 <= 0;

ri scaled shifted d2 <= 0;

end

else

rr scaled shifted d1 <= rr scaled shifted;

ri scaled shifted d1 <= ri scaled shifted;

rr scaled shifted d2 <= rr scaled shifted d1;

ri scaled shifted_d2 <= ri_scaled_shifted_d1;

end

end

```

```

initial

begin

module fft small tb;

data rf = $fopen("real input.txt", "r");

data if = $fopen("imag input.txt","r");

// Input Signals

fft rf = $fopen("real output ver.txt");

fft if = $fopen("imag output ver.txt");

reg clk;

expf = $fopen("exponent output ver.txt");

reg reset;

#0 clk = 1'b0;

reg [15:0] data real in;

#0 reset = 1'b1;

reg [15:0] data imag in;

#92 reset = 1'b0;

reg master sink dav;

reg master sink sop;

reg master source dav;

// Clock Generation

wire inv i;

begin

// Output Signals

#5 clk = 1'b1;

wire [15:0] fft real out;

#5 clk = 1'b0;

end

wire [15:0] fft imag out;

wire [5:0] exponent out;

wire master sink ena;

// Set FFT Direction

// '0' => FFT

wire master source ena;

// '1' => IFFT

wire master source sop;

assign inv i = 1'b0;

wire master source eop;

reg master sink ena reg;

reg [13:0] counter;

integer data real in int,data imag in int,data rf,data if;

integer fft real out int, fft imag out int, exponent out int;

integer fft rf, fft if, expf;

```

### Finally, parts of the test bench

```

integer rc x;

integer ic x;

always @ (negedge clk)

if(reset==1'b1)

begin

data real in<=0;

data imag in<=0;

end

else

if (master sink ena reg==1'b1)

begin

rc x = $fscanf(data rf, "%d", data real in int);

data real in <= data real in int;

ic x = $fscanf(data if, "%d", data imag in int);

data imag in <= data imag in int;

else.

data real in <= data real in;

data imag in <= data imag in;

end

end

end

```

## Conclusion/Next Class

- Today we have been introduced to the history and place of HDLs in the design process

- We have looked at a simple tutorial example to get a feel for the syntax

- We have "glanced" at some examples to get a feel for what is required to design systems in HDL

- Tomorrow we will look at the processes of synthesis (from HDL) and layout on the fabric