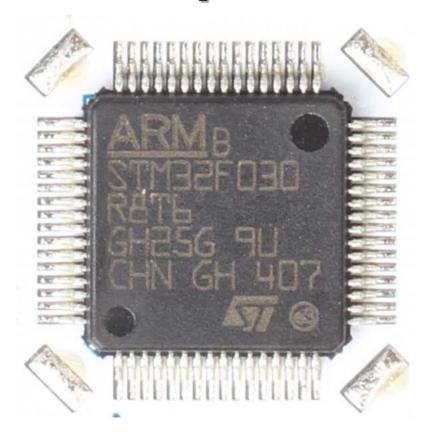

**ARM I/O 101**

November 14, 2017 FRED EADY

### Practical CMSIS

```

* @file stm32f030x8.h

* @author MCD Application Team

* @version V2.2.3

* @date 29-January-2016

* @brief CMSIS Cortex-M0 Device Peripheral Access Layer Header File.

* This file contains all the peripheral register's definitions, bits definitions and memory mapping for STM32F0xx devices.

* This file contains:

* Data structures and the address mapping for all peripherals

* Peripheral's registers declarations and bits definition

* Macros to access peripheral's registers hardware

*

```

## Practical CMSIS

#### **RCC – Reset and Clock Control**

```

326

typedef struct

327 - {

328

IO uint32 t CR;

/*!< RCC clock control register,</pre>

Address offset: 0x00 */

IO uint32 t CFGR;

Address offset: 0x04 */

329

/*!< RCC clock configuration register,</pre>

330

/*!< RCC clock interrupt register,</pre>

Address offset: 0x08 */

IO uint32 t CIR;

/*!< RCC APB2 peripheral reset register,

Address offset: 0x0C */

331

IO uint32 t APB2RSTR;

/*!< RCC APB1 peripheral reset register,

Address offset: 0x10 */

332

IO uint32 t APB1RSTR;

IO uint32 t AHBENR; /*! < RCC AHB peripheral clock register,

333

Address offset: 0x14 */

__IO uint32_t APB2ENR; /*!< RCC APB2 peripheral clock enable register,

334

Address offset: 0x18 */

IO uint32 t APB1ENR; /*! < RCC APB1 peripheral clock enable register,

335

Address offset: 0x1C */

IO uint32 t BDCR;

/*!< RCC Backup domain control register,</pre>

Address offset: 0x20 */

336

IO uint32 t CSR;

/*!< RCC clock control & status register,</pre>

Address offset: 0x24 */

337

IO uint32 t AHBRSTR; /*!< RCC AHB peripheral reset register,

Address offset: 0x28 */

338

339

Address offset: 0x2C */

Address offset: 0x30 */

340

341

IO uint32 t CR2; /*!< RCC clock control register 2,

Address offset: 0x34 */

342

} RCC TypeDef;

#define RCC BASE

(AHBPERIPH BASE + 0x00001000)

495

#define FLASH R BASE

(AHBPERIPH BASE + 0x00002000) /*!< FLASH registers base address */

496

#define OB BASE

((uint32 t)0x1FFFF800U)

/*!< FLASH Option Bytes base address */</pre>

/*!< FLASH Size register base address */

497

#define FLASHSIZE BASE

((uint32 t)0x1FFFF7CCU)

498

#define UID BASE

((uint32 t)0x1FFFF7ACU)

/*!< Unique device ID register base address */</pre>

499

#define CRC BASE

(AHBPERIPH BASE + 0 \times 00003000)

500

501

/*!< AHB2 peripherals */</pre>

502

#define GPIOA BASE

(AHB2PERIPH BASE + 0x000000000)

503

#define GPIOB BASE

(AHB2PERIPH BASE + 0x000000400)

504

#define GPIOC BASE

(AHB2PERIPH BASE + 0x00000800)

505

#define GPIOD BASE

(AHB2PERIPH BASE + 0x00000C00)

(AHB2PERIPH BASE + 0x00001400)

506

#define GPIOF BASE

```

## Practical CMSIS

#### Flash

```

typedef struct

225 🖹 {

226

/*!<FLASH access control register,

Address offset: 0x00 */

IO uint32 t ACR;

IO uint32 t KEYR;

/*!<FLASH kev register.

Address offset: 0x04 */

228

IO uint32 t OPTKEYR;

/*!<FLASH OPT key register,

Address offset: 0x08 */

229

IO uint32 t SR;

/*!<FLASH status register,</pre>

Address offset: 0x0C */

IO uint32 t CR;

230

/*!<FLASH control register,</pre>

Address offset: 0x10 */

IO uint32 t AR;

231

/*!<FLASH address register,</pre>

Address offset: 0x14 */

232

IO uint32 t RESERVED;

/*!< Reserved.</pre>

0x18 */

233

IO uint32 t OBR;

/*!<FLASH option bytes register,</pre>

Address offset: 0x1C */

234

IO uint32 t WRPR;

/*!<FLASH option bytes register,</pre>

Address offset: 0x20 */

} FLASH TypeDef;

235

```

```

#define RCC BASE

(AHBPERIPH BASE + 0 \times 00001000)

(AHBPERIPH BASE + 0x00002000) /*!< FLASH registers base address */

495

#define FLASH R BASE

((uint32 t)0x1FFFF800U) /*!< FLASH Option Bytes base address */

496

#define OB BASE

((uint32 t) 0x1FFFF7CCU) /*!< FLASH Size register base address */

497

#define FLASHSIZE BASE

((uint32 t) 0x1FFFF7ACU) /*!< Unique device ID register base address */

498

#define UID BASE

(AHBPERIPH BASE + 0x00003000)

#define CRC BASE

499

500

/*!< AHB2 peripherals */</pre>

501

(AHB2PERIPH BASE + 0x000000000)

502

#define GPIOA BASE

503

#define GPIOB BASE

(AHB2PERIPH BASE + 0x00000400)

504

#define GPIOC BASE

(AHB2PERIPH BASE + 0x00000800)

505

#define GPIOD BASE

(AHB2PERIPH BASE + 0x00000C00)

#define GPIOF BASE

(AHB2PERIPH BASE + 0x00001400)

506

```

## Practical CMSIS

#### **GPIO – General Purpose Input/Output**

```

typedef struct

255 □ {

IO uint32 t MODER;

256

Address offset: 0x00

/*!< GPIO port mode register,</pre>

257

IO uint32 t OTYPER;

/*!< GPIO port output type register,</pre>

Address offset: 0x04

__IO uint32 t OSPEEDR;

258

/*!< GPIO port output speed register,</pre>

Address offset: 0x08

259

IO uint32 t PUPDR;

/*!< GPIO port pull-up/pull-down register,</pre>

Address offset: 0x0C

IO uint32 t IDR;

/*!< GPIO port input data register,</pre>

260

Address offset: 0x10

__IO uint32 t ODR;

261

/*!< GPIO port output data register,</pre>

Address offset: 0x14

/*!< GPIO port bit set/reset register,</pre>

262

IO uint32 t BSRR;

Address offset: 0x1A */

263

IO uint32 t LCKR:

/*!< GPIO port configuration lock register,</pre>

Address offset: 0x1C

__IO uint32_t AFR[2]; /*!< GPIO alternate function low register, Address offset: 0x20-0x24 */

264

/*!< GPIO bit reset register.</pre>

265

IO uint32 t BRR;

Address offset: 0x28

*/

266

} GPIO TypeDef;

```

```

#define RCC BASE

(AHBPERIPH BASE + 0 \times 000001000)

#define FLASH R BASE

(AHBPERIPH BASE + 0x00002000) /*!< FLASH registers base address */

495

((uint32 t) 0x1FFFF800U) /*!< FLASH Option Bytes base address */

496

#define OB BASE

/*!< FLASH Size register base address */

497

#define FLASHSIZE BASE

((uint32 t)0x1FFFF7CCU)

((uint32 t) 0x1FFFF7ACU) /*!< Unique device ID register base address */

498

#define UID BASE

499

#define CRC BASE

(AHBPERIPH BASE + 0 \times 000003000)

500

/*!< AHB2 peripherals */</pre>

501

502

#define GPIOA BASE

(AHB2PERIPH BASE + 0x000000000)

503

#define GPIOB BASE

(AHB2PERIPH BASE + 0x00000400)

504

#define GPIOC BASE

(AHB2PERIPH BASE + 0x00000800)

(AHB2PERIPH BASE + 0x00000C00)

505

#define GPIOD BASE

#define GPIOF BASE

(AHB2PERIPH BASE + 0 \times 00001400)

506

```

## Practical CMSIS

### **Peripheral Declarations**

```

#define FLASH

((FLASH TypeDef *) FLASH R BASE)

546

#define OB

((OB TypeDef *) OB BASE)

((RCC TypeDef *) RCC BASE)

547 #define RCC

548 #define CRC

((CRC TypeDef *) CRC BASE)

((GPIO TypeDef *) GPIOA BASE)

549 #define GPIOA

550 #define GPIOB

((GPIO TypeDef *) GPIOB BASE)

551 #define GPIOC

((GPIO TypeDef *) GPIOC BASE)

552

#define GPIOD

((GPIO TypeDef *) GPIOD BASE)

((GPIO TypeDef *) GPIOF BASE)

553 #define GPIOF

```

### To Set I/O PIN PA.5 as OUTPUT-

Instead of: (\*GPIOA).MODER |= (GPIO\_MODER\_MODER5\_0);

We use: GPIOA->MODER |= (GPIO\_MODER\_MODER5\_0);

# **GPIO** Fundamentals

#### 8.4.1 GPIO port mode register (GPIOx\_MODER) (x =A..F)

Address offset:0x00

#### Reset values:

- 0x2800 0000 for port A

- 0x0000 0000 for other ports

| 31    | 30       | . 29  | 28       | . 21 | 26       | . 25 | 24       | . 23 | 22       | . 21 | 20       | . 19 | 18      | 17   | 16      |

|-------|----------|-------|----------|------|----------|------|----------|------|----------|------|----------|------|---------|------|---------|

| MODER | R15[1:0] | MODER | R14[1:0] | MODE | R13[1:0] | MODE | R12[1:0] | MODE | R11[1:0] | MODE | R10[1:0] | MODE | R9[1:0] | MODE | R8[1:0] |

| rw    | rw       | rw    | rw       | rw   | rw       | rw   | rw       | rw   | rw       | rw   | rw       | rw   | rw      | rw   | rw      |

| 15    | 14       | 13    | 12       | 11   | 10       | 9    | 8        | 7    | 6        | 5    | 4        | 3    | 2       | 1    | 0       |

| MODE  | R7[1:0]  | MODE  | R6[1:0]  | MODE | R5[1:0]  | MODE | R4[1:0]  | MODE | R3[1:0]  | MODE | R2[1:0]  | MODE | R1[1:0] | MODE | R0[1:0] |

| rw    | rw       | rw    | rw       | rw   | rw       | rw   | rw       | rw   | rw       | rw   | rw       | rw   | rw      | rw   | rw      |

Bits 2y+1:2y **MODERy[1:0]:** Port x configuration bits (y = 0..15)

These bits are written by software to configure the I/O mode.

00: Input mode (reset state)

01: General purpose output mode

10: Alternate function mode

11: Analog mode

# **GPIO** Fundamentals

#### 8.4.2 GPIO port output type register (GPIOx\_OTYPER) (x = A..F)

Address offset: 0x04

Reset value: 0x0000 0000

| 31         | 30         | 29         | 28         | 27         | 26         | 25       | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------|------------|------------|------------|------------|------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Res.       | Res.       | Res.       | Res.       | Res.       | Res.       | Res.     | Res.     | Res.     | Res.     | Res.     | Res.     | Res.     | Res.     | Res.     | Res.     |

|            |            |            |            |            |            |          |          |          |          |          |          |          |          |          |          |

|            |            |            |            |            |            |          |          |          |          |          |          |          |          |          |          |

| 15         | 14         | 13         | 12         | 11         | 10         | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

| 15<br>OT15 | 14<br>OT14 | 13<br>OT13 | 12<br>OT12 | 11<br>OT11 | 10<br>OT10 | 9<br>OT9 | 8<br>OT8 | 7<br>OT7 | 6<br>OT6 | 5<br>OT5 | 4<br>OT4 | 3<br>OT3 | 2<br>OT2 | 1<br>OT1 | 0<br>OT0 |

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 **OTy:** Port x configuration bits (y = 0..15)

These bits are written by software to configure the I/O output type.

0: Output push-pull (reset state)

1: Output open-drain

# **GPIO** Fundamentals

# 8.4.4 GPIO port pull-up/pull-down register (GPIOx\_PUPDR) (x = A..F)

Address offset: 0x0C

Reset values:

- 0x2400 0000 for port A

- 0x0000 0000 for other ports

| 31    | 30       | 29    | 28       | 27    | 26       | 25    | 24       | 23    | 22       | 21    | 20       | 19   | 18      | 17    | 16      |

|-------|----------|-------|----------|-------|----------|-------|----------|-------|----------|-------|----------|------|---------|-------|---------|

| PUPDF | R15[1:0] | PUPDF | R14[1:0] | PUPDF | R13[1:0] | PUPDF | R12[1:0] | PUPDF | R11[1:0] | PUPDF | R10[1:0] | PUPD | R9[1:0] | PUPDE | R8[1:0] |

| rw    | rw       | rw   | rw      | rw    | rw      |

| 15    | 14       | 13    | 12       | 11    | 10       | 9     | 8        | 7     | 6        | 5     | 4        | 3    | 2       | 1     | 0       |

| PUPD  | R7[1:0]  | PUPDI | R6[1:0]  | PUPDI | R5[1:0]  | PUPDI | R4[1:0]  | PUPDI | R3[1:0]  | PUPDI | R2[1:0]  | PUPD | R1[1:0] | PUPDE | R0[1:0] |

| rw    | rw       | rw   | rw      | rw    | rw      |

Bits 2y+1:2y **PUPDRy[1:0]:** Port x configuration bits (y = 0..15)

These bits are written by software to configure the I/O pull-up or pull-down

00: No pull-up, pull-down

01: Pull-up 10: Pull-down

10: Pull-down

# **GPIO** Fundamentals

# 8.4.3 GPIO port output speed register (GPIOx\_OSPEEDR) (x = A..F)

Address offset: 0x08

Reset value:

- 0x0C00 0000 for port A

- 0x0000 0000 for other ports

| 31 | 30           | 29 | 28           | 27 | 26           | 25 | 24           | 23 | 22           | 21 | 20           | 19 | 18          | 17 | 16          |

|----|--------------|----|--------------|----|--------------|----|--------------|----|--------------|----|--------------|----|-------------|----|-------------|

|    | EDR15<br>:0] |    | EDR14<br>:0] |    | EDR13<br>:0] |    | EDR12<br>:0] |    | EDR11<br>:0] |    | EDR10<br>:0] |    | EDR9<br>:0] |    | EDR8<br>:0] |

| rw | rw           | rw | rw          | rw | rw          |

| 15 | 14           | 13 | 12           | 11 | 10           | 9  | 8            | 7  | 6            | 5  | 4            | 3  | 2           | 1  | 0           |

|    | EDR7<br>:0]  |    | EDR6<br>:0]  |    | EDR5<br>:0]  |    | EDR4<br>:0]  |    | EDR3<br>:0]  |    | EDR2<br>:0]  |    | EDR1<br>:0] | ı  | EDR0<br>:0] |

| rw | rw           | rw | rw          | rw | rw          |

Bits 2y+1:2y **OSPEEDRy[1:0]**: Port x configuration bits (y = 0..15)

These bits are written by software to configure the I/O output speed.

x0: Low speed 01: Medium speed

11: High speed

Note: Refer to the device datasheet for the frequency specifications and the power supply and load conditions for each speed.

# **GPIO** Fundamentals

### 8.4.7 GPIO port bit set/reset register (GPIOx\_BSRR) (x = A..F)

Address offset: 0x18

Reset value: 0x0000 0000

| 31   | 30   | 29   | 28   | 27   | 26   | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BR15 | BR14 | BR13 | BR12 | BR11 | BR10 | BR9 | BR8 | BR7 | BR6 | BR5 | BR4 | BR3 | BR2 | BR1 | BR0 |

| w    | w    | w    | w    | w    | w    | w   | w   | w   | w   | w   | W   | W   | w   | w   | w   |

| 15   | 14   | 13   | 12   | 44   | 40   | _   |     |     |     |     | 4   | 2   | 2   | 4   |     |

|      | . 14 | . 13 | . 12 |      | 10   | 9   | 8   | . / | . 6 | 5   | . 4 | 3   | . 2 | . 1 | U   |

| BS15 | BS14 | BS13 | BS12 | BS11 | BS10 | BS9 | BS8 | BS7 | BS6 | BS5 | BS4 | BS3 | BS2 | BS1 | BS0 |

#### 8.4.11 GPIO port bit reset register (GPIOx\_BRR) (x =A..F)

Address offset: 0x28

Reset value: 0x0000 0000

| 31         | 30         | 29         | 28         | 27         | 26         | 25       | 24       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       |

|------------|------------|------------|------------|------------|------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Res.       | Res.       | Res.       | Res.       | Res.       | Res.       | Res.     | Res.     | Res.     | Res.     | Res.     | Res.     | Res.     | Res.     | Res.     | Res.     |

|            |            |            |            |            |            |          |          |          |          |          |          |          |          |          |          |

|            |            |            |            |            |            |          |          |          |          |          |          |          |          |          |          |

| 15         | 14         | 13         | 12         | 11         | 10         | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

| 15<br>BR15 | 14<br>BR14 | 13<br>BR13 | 12<br>BR12 | 11<br>BR11 | 10<br>BR10 | 9<br>BR9 | 8<br>BR8 | 7<br>BR7 | 6<br>BR6 | 5<br>BR5 | 4<br>BR4 | 3<br>BR3 | 2<br>BR2 | 1<br>BR1 | 0<br>BR0 |

# **GPIO** Fundamentals

```

309

310

311

void initGPIO(void)

312 - {

313

//enable PORTA -PORTB - PORTC GPIO Clocks

314

RCC->AHBENR |= (RCC_AHBENR_GPIOAEN | RCC_AHBENR_GPIOBEN | RCC_AHBENR_GPIOCEN);

315

//setup PA.5 - Green LED

GPIOA->MODER &= ~ (GPIO MODER MODER5);

316

317

GPIOA->MODER |= (GPIO MODER MODER5 0);

318

GPIOA->OTYPER &= ~(GPIO OTYPER OT 5);

319

GPIOA->OSPEEDR &= ~(GPIO OSPEEDER OSPEEDR5);

320

GPIOA->OSPEEDR |= (GPIO OSPEEDER OSPEEDR5 0);

321

GPIOA->PUPDR &= ~(GPIO PUPDR PUPDR5);

322

//setup PB.4-7 - LCD Data

323

GPIOB->MODER &= ~ (GPIO_MODER_MODER4 | GPIO_MODER_MODER5 | GPIO_MODER_MODER6 | GPIO_MODER_MODER7);

324

GPIOB->MODER |= (GPIO MODER MODER4 0 | GPIO MODER MODER5 0 | GPIO MODER MODER6 0 | GPIO MODER MODER7 0);

GPIOB->OTYPER &= ~(GPIO_OTYPER_OT_4 | GPIO_OTYPER_OT_5 | GPIO_OTYPER_OT_6 | GPIO_OTYPER_OT_7);

325

GPIOB->OSPEEDR &= ~(GPIO OSPEEDR OSPEEDR4 | GPIO OSPEEDR OSPEEDR5 | GPIO OSPEEDR OSPEEDR6 | GPIO OSPEEDR OSPEEDR7);

326

GPIOB->OSPEEDR |= (GPIO_OSPEEDR_OSPEEDR4_0 | GPIO_OSPEEDR_OSPEEDR5_0 | GPIO_OSPEEDR_OSPEEDR6_0 | GPIO_OSPEEDR6_0);

327

GPIOB->PUPDR &= ~(GPIO_PUPDR_PUPDR4 | GPIO_PUPDR_PUPDR5 | GPIO_PUPDR_PUPDR6 | GPIO_PUPDR_PUPDR7);

328

//setup PC.5 - PC.6 - PC.8 - LCD Control

329

330

GPIOC->MODER &= ~(GPIO MODER MODER5 | GPIO_MODER_MODER6 | GPIO_MODER_MODER8);

GPIOC->MODER |= (GPIO MODER MODERS 0 | GPIO MODER MODER6 0 | GPIO MODER MODER8 0);

331

332

GPIOC->OTYPER &= ~(GPIO OTYPER OT 5 | GPIO OTYPER OT 6 | GPIO OTYPER OT 8);

GPIOC->OSPEEDR &= ~(GPIO_OSPEEDR_OSPEEDRS | GPIO_OSPEEDRO OSPEEDR6 | GPIO_OSPEEDR OSPEEDR8);

333

GPIOC->OSPEEDR |= (GPIO_OSPEEDR_OSPEEDR5_0 | GPIO_OSPEEDR_OSPEEDR6_0 | GPIO_OSPEEDR_OSPEEDR8_0);

334

GPIOC->PUPDR &= ~(GPIO PUPDR PUPDR5 | GPIO PUPDR PUPDR6 | GPIO PUPDR PUPDR8);

335

336 -}

```

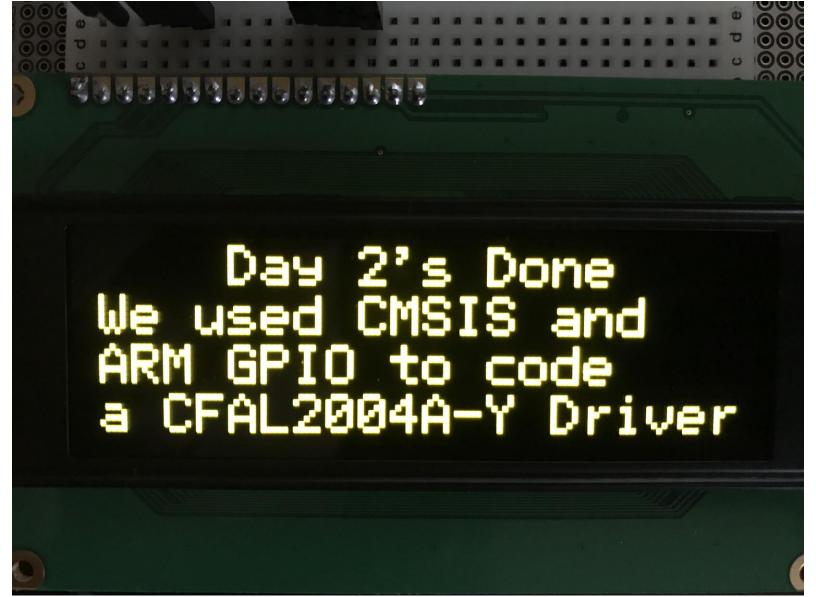

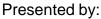

# A CFAL2004A-Y Driver

```

//*

FUNCTION PROTOTYPES

void delay_us_us(uint32_t dlyTicks);

void lcd send cmd nibble(uint8 t bite);

void lcd send cmd byte(uint8 t bite);

void lcd send_data_nibble(uint8_t bite);

void lcd send_data_byte(uint8_t bite);

void lcd_writel(uint8_t *dstr);

void lcd write2(uint8 t *dstr);

void lcd write3(uint8 t *dstr);

void lcd write4(uint8 t *dstr);

24 | void lcd init(void);

void chkBusy(void);

27  #define lcdDataMask 0x00F0

29 | //E - PC5

30 | #define Ehi GPIO BSRR BS 5

GPIO BRR BR 5

#define Elo

//RS - PC8

33 | #define RShi GPIO BSRR BS 8

34 | #define RSlo GPIO BRR BR 8

35 //RW - PC6

36 | #define RWhi GPIO BSRR BS 6

37 | #define RWlo GPIO BRR BR 6

38

39

#define setRW GPIOC->BSRR = RWhi

41 | #define clrRW GPIOC->BRR = RWlo

42 #define setRS GPIOC->BSRR = RShi

43 | #define clrRS GPIOC->BRR = RSlo

44 | #define setE GPIOC->BSRR = Ehi

45 #define clrE GPIOC->BRR = Elo

```

lcd.h Function Prototypes RS-RW-E Definitions Bit Set/Reset Macros

## A CFAL2004A-Y Driver

```

34 //* SystemCoreClockConfigure:

35 //* Configure SystemCoreClock using HSI

36 //* HSE is not populated on Nucleo board

37 //***********************

void SystemCoreClockConfigure(void)

39 □ {

RCC->CR |= ((uint32 t)RCC CR HSION);

40

// Enable HSI

while ((RCC->CR & RCC CR HSIRDY) == 0);

// Wait for HSI Ready

41

42

43

RCC->CFGR = RCC CFGR SW HSI;

// HSI is system clock

while ((RCC->CFGR & RCC CFGR SWS) != RCC CFGR SWS HSI); // Wait for HSI used as system clock

45

46

FLASH->ACR = FLASH ACR PRFTBE;

// Enable Prefetch Buffer

FLASH->ACR |= FLASH ACR LATENCY;

47

// Flash 1 wait state

48

RCC->CFGR |= RCC CFGR HPRE DIV1;

// HCLK = SYSCLK

49

RCC->CFGR |= RCC CFGR PPRE DIV1;

50

// PCLK = HCLK

51

52

RCC->CR &= ~RCC CR PLLON;

// Disable PLL

53

54

//PLL configuration: = HSI/2 * 12 = 48 MHz

RCC->CFGR &= ~(RCC CFGR PLLSRC | RCC CFGR PLLXTPRE | RCC CFGR PLLMUL);

55

//HSI used as PLL clock source : SystemCoreClock = HSI/2 * PLLMUL

56

RCC->CFGR |= (RCC CFGR PLLSRC HSI DIV2 | RCC CFGR PLLMUL12);

57

58

59

60

RCC->CR |= RCC CR PLLON;

// Enable PLL

while((RCC->CR & RCC CR PLLRDY) == 0) NOP();

61

// Wait till PLL is ready

62

RCC->CFGR &= ~RCC CFGR SW;

63

// Select PLL as system clock source

RCC->CFGR |= RCC CFGR SW PLL;

64

while ((RCC->CFGR & RCC CFGR SWS) != RCC CFGR SWS PLL); // Wait till PLL is system clock src

66 -}

```

## A CFAL2004A-Y Driver

```

19 //* SysTick Handler

21 void SysTick Handler (void)

22 ⊟ {

23

usTicks++;

24 -1

26 //* Delay Microseconds

28 -void delay us (uint32 t dlyTicks) {

uint32 t curTicks;

29

30

31

curTicks = usTicks;

while ((usTicks - curTicks) < dlyTicks) { NOP(); }</pre>

33 -}

343 //* MAIN - Display Messages

345

int main (void)

346 ⊟ {

347

SystemCoreClockConfigure();

// configure HSI as System Clock

348

SystemCoreClockUpdate();

SysTick Config(SystemCoreClock / 1000000); // SysTick 1 uS interrupts

349

```

# A CFAL2004A-Y Driver

```

//* SEND CMD NIBBLE

87

void lcd_send_cmd_nibble(uint8_t bite)

88 🗏 {

89

clrE;

90

clrRS;

91

GPIOB->ODR &= ~(lcdDataMask);

92

GPIOB->ODR |= (bite & 0xF0);

93

setE;

94

delay us(1);

95

clrE;

96

97

//* SEND CMD BYTE

void lcd_send_cmd_byte(uint8_t bite)

101 - {

102

chkBusy();

103

lcd send cmd nibble(bite);

104

lcd send cmd nibble(bite << 4);</pre>

105 -}

106

//* SEND DATA NIBBLE

void lcd send data nibble(uint8 t bite)

110 - {

111

clrE;

112

setRS:

113

GPIOB->ODR &= ~(lcdDataMask);

114

GPIOB->ODR |= (bite & 0xF0);

115

setE:

116

delay_us(1);

117

118

//* SEND DATA BYTE

void lcd send data byte(uint8 t bite)

123 - {

124

chkBusy();

125

lcd send data nibble(bite);

126

lcd send data nibble(bite << 4);</pre>

127 -}

```

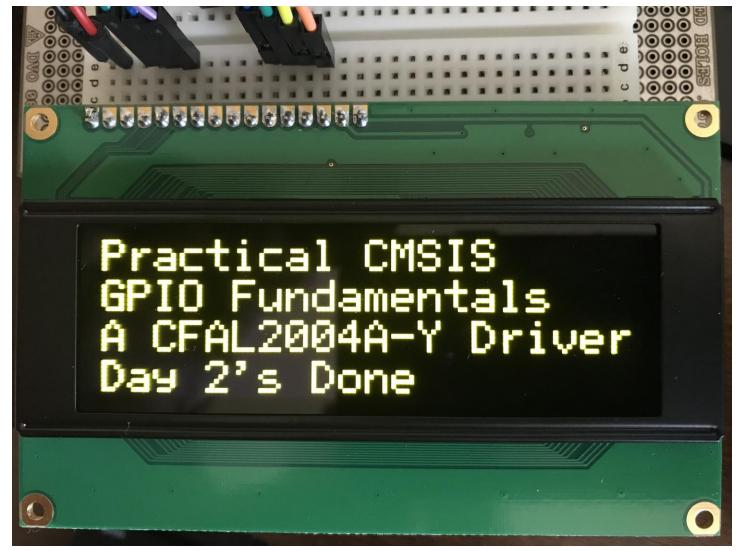

## A CFAL2004A-Y Driver

```

68

69

LCD MESSAGES

72 uint8 t msgCec[] =

"CEC ARM GPIO Primer ";

73 uint8 t msgDK[] = "Hosted By Digi-Key ";

74 uint8 t msgLcd[] =

"CFAL2004A-Y Driver ";

75 uint8 t msgNuc[] = "STM32F030R8 Version ";

76  uint8 t msgAgnl[] = "Practical CMSIS

77 uint8 t msgAgn2[] = "GPIO Fundamentals

78 uint8 t msgAgn3[] = "a CFAL2004A-Y Driver";

79 uint8 t msgAgn4[] = " Day 2's Done

80 uint8 t msgdoth[] =

"lcd.h

81 uint8 t msgcnt0[] = "Function Prototypes";

82 uint8 t msgcntl[] = "RS-RW-E Definitions";

83 uint8 t msqcnt2[] =

"Bit Set/Reset Macros":

348 //*

349 //* MAIN - Display Messages

350

351 int main (void)

352 □ {

// configure HSI as System Clock

353

SystemCoreClockConfigure():

354

SystemCoreClockUpdate();

355

SysTick Config(SystemCoreClock / 1000000); // SysTick 1 uS interrupts

356

357

initGPIO();

358

initLCD();

359

360

lcd writel(msgCec);

361

lcd write2(msgDK);

362

lcd write3(msgLcd);

lcd write4(msgNuc);

363

364

while(1);

365 }

```

**DesignNews**